إنتل هو الكل في توصيل الطاقة الخلفية

هناك الكثير من المخاطر في نشر التكنولوجيا الجديدة لرقائق الكمبيوتر المتطورة. لذلك كان التنفيذيون في إنتل حذرين بشكل مفهوم في تنفيذ خطة تقدم العام المقبل في نفس الوقت كلاً من ترانزستور جديد – RibbonFET – وطريقة جديدة لتشغيله – PowerVia.

للتخلص من بعض المخاطر من هذا العمل عالي الأسلاك ، قامت الشركة ببناء واختبار نوى المعالجات المكونة من الجيل الحالي من Intel من الترانزستورات جنبًا إلى جنب مع PowerVia. شهدت النوى الناتجة زيادة في التردد بنسبة تزيد عن 6 بالمائة بالإضافة إلى تصميمات أكثر إحكاما وفقدان طاقة أقل بنسبة 30 بالمائة. وبنفس القدر من الأهمية ، أثبتت الاختبارات أن تضمين القوة الخلفية لا يجعل الرقائق أكثر تكلفة أو أقل موثوقية أو يصعب اختبارها بحثًا عن العيوب. تقدم إنتل تفاصيل هذه الاختبارات في طوكيو الأسبوع المقبل في ندوة IEEE حول تكنولوجيا VLSI والدوائر.

يقول بن سيل ، نائب رئيس تطوير التكنولوجيا بشركة إنتل: “أردنا التأكد من أننا يمكن أن نخرج … فهم كل شيء عن PowerVia ، ثم ننتقل إلى الخطوة التالية ونتكامل مع RibbonFET”.

PowerVia هو إصدار Intel من تقنية تسمى توصيل الطاقة الخلفية. اليوم ، تُصنع الرقائق باستخدام الترانزستورات الموجودة على سطح السيليكون وجميع الوصلات التي تشغلها وتنقل إشارات بياناتها المبنية فوقها. تعمل الطاقة الخلفية على إزالة جميع الوصلات البينية التي توفر الطاقة أسفل السيليكون. هذا له تأثيران رئيسيان. أولاً ، يترك مساحة أكبر لربط البيانات فوق السيليكون. وثانيًا ، يمكن جعل وصلات الطاقة أكبر وبالتالي أقل مقاومة.

يعمل توصيل الطاقة الخلفية على نقل وصلات الطاقة من أعلى السيليكون إلى أسفله.شركة انتل

هذا المزيج يحسن الأداء بعدة طرق. أولاً ، مع وجود مسار أسهل لتدفق الطاقة ، تعاني الدوائر الموجودة على وحدة المعالجة المركزية من انخفاض الجهد الكهربائي ؛ بعبارة أخرى ، هناك انخفاض عابر أصغر في الجهد عندما يزداد الطلب على التيار ، على سبيل المثال ، من كتلة كبيرة من التبديل المنطقي. مع تدلى أقل ، يمكن تشغيل الترانزستورات بشكل أسرع.

ثانيًا ، يمكن جعل النوى أكثر إحكاما ، مما يقلل من طول الترابط بين الخلايا المنطقية ، مما يؤدي إلى تسريع الأمور. عندما يتم وضع الخلايا المنطقية القياسية التي تشكل قلب المعالج على الشريحة ، فإن ازدحام الاتصال يمنعها من التعبئة معًا بشكل مثالي ، مما يترك الكثير من المساحة الفارغة بين الخلايا. مع تقليل الازدحام بين روابط البيانات ، تتلاءم الخلايا معًا بشكل أكثر إحكامًا ، مع ملء بعض الأجزاء حتى 95 بالمائة. يقول سيل أن هذا تحسن من رقمين. علاوة على ذلك ، سمح عدم وجود ازدحام ببعض أصغر الوصلات البينية بالانتشار قليلاً ، مما قلل من السعة الطفيلية التي تعيق الأداء.

المكاسب البالغة 6 في المائة من هذه المزايا هي حوالي نصف ما يتم تسليمه عادةً عندما يقوم صانع الرقائق بتقليص الترانزستورات من عقدة تقنية إلى أخرى. تقوم PowerVia بتوصيلها دون تغيير في الترانزستورات.

كيف يتم صنع PowerVia

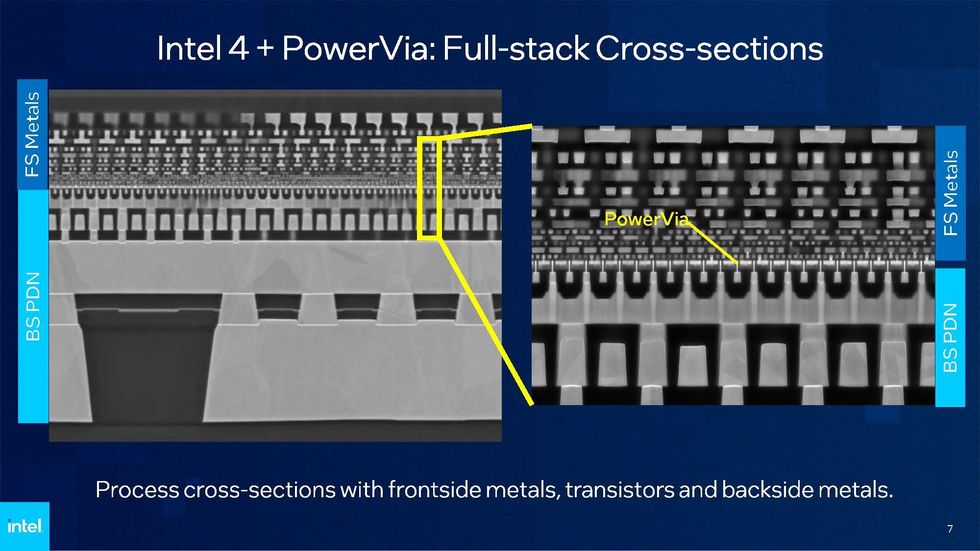

يتطلب صنع رقائق تدعم PowerVia عدة خطوات إضافية ويؤدي إلى نتيجة غير عادية وهي أنه لم يتبق أي سيليكون في الشريحة. تبدأ الأمور بشكل طبيعي: الترانزستورات ، والتي في هذه الحالة هي FinFETs مصنوعة باستخدام عملية Intel 4 ، يتم بناؤها على سطح السيليكون ، كالمعتاد. الفرق الرئيسي هو أنه يتم حفر مجموعة من الثقوب العميقة والضيقة أيضًا ثم ملؤها بالمعدن. ستكون مركبات TSV النانوية هذه (من خلال فتحات السليكون) مهمة في وقت لاحق. من هناك ، تتشكل طبقات من الترابط فوق الترانزستورات لربطها معًا في خلايا منطقية ودوائر أكبر. حتى الآن ، منتظم جدا.

ثم تأخذ العملية منعطفا. يتم ربط رقاقة سيليكون فارغة ، تسمى رقاقة حاملة ، بأعلى تلك الوصلات البينية ويتم قلب كل شيء. ثم يتم تلميع الجزء السفلي من الرقاقة الأصلية (الآن في الأعلى) بعيدًا حتى تنكشف نهايات nano-TSVs. عند هذه النقطة ، يتم بناء طبقات من الوصلات البينية الكثيفة نسبيًا للاتصال بـ nano-TSVs وتشكيل شبكة توصيل الطاقة الخلفية. تنتهي طبقات الترابط هذه في وسادات الرابطة التي ستربط الشريحة بالحزمة وبقية الكمبيوتر.

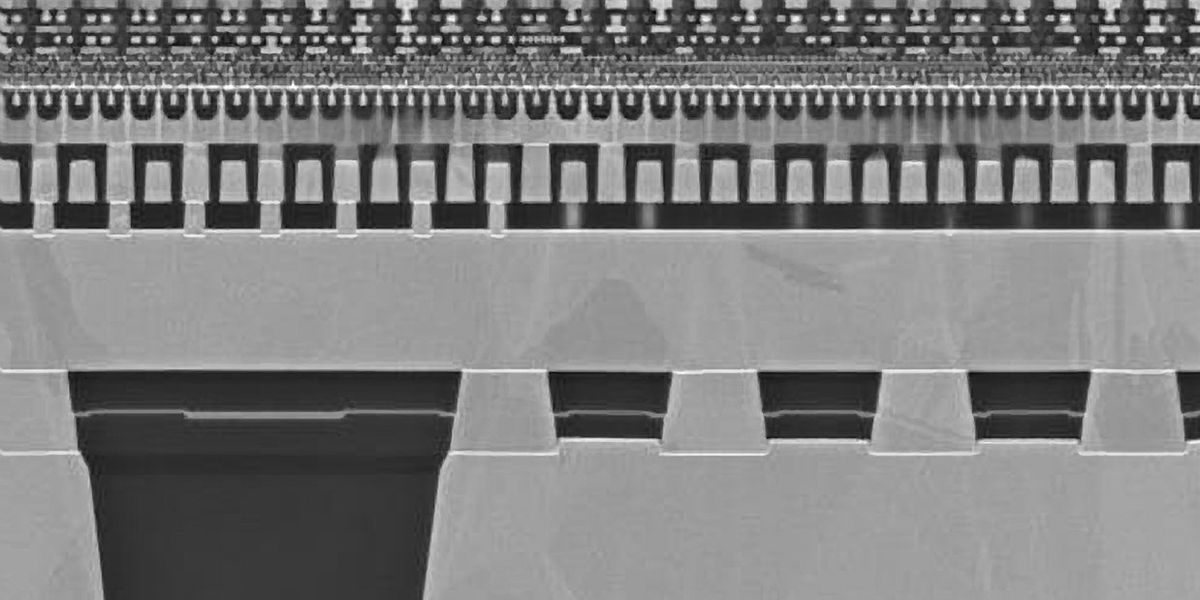

وهكذا تتكون الشريحة الناتجة من طبقة كبيرة من السيليكون الفارغ للدعم ، وطبقة من روابط البيانات ، وطبقة ضيقة من ترانزستورات السيليكون ، وطبقة من وصلات الطاقة.

من الصعب اكتشاف السيليكون في هذا المعالج المزود بتقنية PowerVia. (تلميح: إنه جزء من اللون الأبيض في المنتصف.) تتكون معظم الشريحة من وصلات الإشارة أعلاه وتوصيلات الطاقة الأكثر كثافة أسفل الترانزستورات. شركة انتل

من الصعب اكتشاف السيليكون في هذا المعالج المزود بتقنية PowerVia. (تلميح: إنه جزء من اللون الأبيض في المنتصف.) تتكون معظم الشريحة من وصلات الإشارة أعلاه وتوصيلات الطاقة الأكثر كثافة أسفل الترانزستورات. شركة انتل

قد تتوقع أن الاضطرار إلى بناء وصلات بينية على جانبي السيليكون سيؤدي إلى ارتفاع تكلفة الشريحة. لكن في وقت مبكر ، رأت إنتل سببًا لعدم حدوث ذلك ، كما يقول سيل. تعتبر الطبقة الأصغر والأكثر حزمًا من الوصلات البينية ، والتي تسمى M0 ، هي أيضًا الأكثر تكلفة من حيث الإنتاج. يمكن أن تتطلب أكثر من تمريرة واحدة من خلال أغلى خطوة في صناعة الرقائق ، وهي الطباعة الحجرية فوق البنفسجية الشديدة. ولكن مع عدم وجود وصلات كهربائية لإعاقة الطريق ، يمكن أن تكون الخطوط الموجودة في الطبقة M0 أبعد بمقدار ستة نانومتر عما هي عليه اليوم. قد لا يبدو هذا كثيرًا ، لكن هذا يعني أن الأمر يتطلب جهدًا أقل من EUV للقيام بها. بالنسبة للعملية التي سيتم تقديمها في العام المقبل وللخلف الذي سيخلفها ، يقول سيل: “إن وفورات التكلفة التي نحصل عليها من عدم التوسع بقوة أكبر من تعويض التكلفة الإضافية من عملية توصيل الطاقة المؤخرة”.

الاستهزاء بالقوة

إذا كانت خطط PowerVia ستنجح ، يجب أن تلبي التكنولوجيا معايير معينة ، معظمها يتعلق بعدم جعل الأمور أسوأ: على الرغم من وجودها في طبقة أرق بكثير من السيليكون ، كان على الترانزستورات أن تعمل بشكل جيد ؛ يجب أن تكون شبكة توصيل الطاقة موثوقة تمامًا مثل تلك المبنية على الجانب الأمامي من السيليكون ؛ الحرارة المتولدة في السيليكون لا يمكن أن تخرج عن السيطرة ، على الرغم من أن الترانزستورات محصورة بين طبقات مترابطة ؛ والقدرة على تصحيح أخطاء الدوائر المتكاملة وتحديد عيوب التصميم لا يمكن إعاقتها.

استغرق الأمر بعض العمل لتلبية هذه المعايير. على سبيل المثال ، كان لا بد من تعديل عملية ربط الطاقة لمنع التأثير على الترانزستورات. وكان على شركة إنتل أن تضع بعض قواعد التصميم لتتماشى مع المشكلات الحرارية. كان عليه أيضًا أن يبتكر طرقًا جديدة لإجراء تصحيح الأخطاء.

علاوة على كل ذلك ، كان على مهندسي إنتل التأكد من أن عائد رقائق PowerVia – جزء الرقائق الجيدة لكل رقاقة – كان على الهدف للوصول إلى تصنيع كبير الحجم ، على الرغم من أن هذه الرقائق المعينة لن تُباع أبدًا. كان الهدف هنا هو إنتاج رقائق Intel 4 PowerVia لتتناسب مع رقائق Intel 4 منذ 9 أشهر. كانت رقائق PowerVia تتأخر دائمًا ، لأن أي تحسينات على إنتاجية Intel 4 ستستغرق وقتًا لترجمتها إلى تجارب PowerVia. يقول سيل: “لقد فعلنا أفضل قليلاً من ذلك”. منحنى عائد PowerVia يتبع Intel 4 بـ 6 أشهر فقط.

2024 وما بعدها

مع نجاح عملية PowerVia ، فإن التغيير الوحيد الذي سيتعين على Intel إجراؤه لإكمال انتقالها من Intel 4 إلى العقدة التالية ، المسماة 20A ، هو الترانزستور. RibbonFET ، التي تتخذها Intel على الترانزستورات النانوية ، أو الترانزستورات الشاملة للبوابة ، ستدخل بعد ذلك في مخطط التوصيل البيني الذي تم إنشاؤه بالفعل.

إذا سارت الأمور على ما يرام ، وقالت سيل إن كل شيء يسير على ما يرام ، فإن عملية 20A ستصنع وحدات المعالجة المركزية Arrow Lake التابعة للشركة في عام 2024. الجيل التكنولوجي التالي ، المسمى 18A ، مخصص لكل من منتجات Intel وعملاء المسابك.

النجاح من شأنه أن يضع Intel في مرتبة متقدمة على TSMC و Samsung ، في تقديم كل من ترانزستورات الصفائح النانوية والطاقة الخلفية. لقد انتقلت Samsung بالفعل إلى جهاز شامل البوابة ، وليس من الواضح متى ستدمج الطاقة الخلفية. من المقرر أن تقدم TSMC أجهزة شاملة للبوابة في عام 2025 ، لكنها لن تضيف توصيل طاقة خلفي حتى عام 2026 على الأقل.

من مقالات موقعك

مقالات ذات صلة حول الويب