إن الإبقاء على قانون مور أمر معقد

كان هناك وقت ، عقود حقًا ، كان كل ما يتطلبه الأمر لصنع شريحة كمبيوتر أفضل هو ترانزستورات أصغر وتوصيلات ضيقة. لقد مضى ذلك الوقت منذ فترة طويلة ، وعلى الرغم من أن الترانزستورات ستستمر في التقلص قليلاً ، إلا أن جعلها هكذا لم يعد هو الهدف. قال باحثون في ITF World 2023 الأسبوع الماضي في أنتويرب ، بلجيكا ، إن الطريقة الوحيدة لمواكبة الوتيرة المتسارعة للحوسبة الآن هي مخطط يسمى التحسين المشترك لتكنولوجيا النظام ، أو STCO. إنها القدرة على تقسيم الرقائق إلى مكوناتها الوظيفية ، واستخدام الترانزستور الأمثل وتقنية التوصيل البيني لكل وظيفة ، وربطها معًا مرة أخرى لإنشاء طاقة أقل ، وكاملة تعمل بشكل أفضل.

تقول ماري جارسيا باردون ، مديرة البحث والتطوير بشركة Imec: “يقودنا هذا إلى نموذج جديد لـ CMOS”. CMOS 2.0 ، كما تسميه منظمة أبحاث تكنولوجيا النانو ومقرها بلجيكا ، هي رؤية معقدة. لكنها قد تكون الطريقة الأكثر عملية للمضي قدمًا ، وأجزاء منها واضحة بالفعل في رقائق اليوم الأكثر تقدمًا.

كيف وصلنا إلى هنا

يقول Julien Ryckaert ، نائب رئيس البحث والتطوير في Imec ، إن صناعة أشباه الموصلات قد أفسدتها إلى حد ما العقود التي سبقت عام 2005 تقريبًا. خلال ذلك الوقت ، كان الكيميائيون وعلماء الأجهزة قادرين على إنتاج ترانزستور أصغر وأسرع وأقل قوة يمكن استخدامه لكل وظيفة على الرقاقة ، وهذا من شأنه أن يؤدي إلى زيادة مطردة في القدرة الحاسوبية. لكن العجلات بدأت تؤتي ثمارها بعد ذلك بوقت قصير. يمكن لمتخصصي الأجهزة أن يبتكروا ترانزستورات جديدة ممتازة ، لكن تلك الترانزستورات لم تكن تصنع دوائر أصغر وأفضل ، مثل ذاكرة SRAM والخلايا المنطقية القياسية التي تشكل الجزء الأكبر من وحدات المعالجة المركزية. رداً على ذلك ، بدأ صانعو الرقائق في كسر الحواجز بين تصميم الخلية القياسي وتطوير الترانزستور. أدى المخطط الجديد الذي أطلق عليه اسم التحسين المشترك لتقنية التصميم ، أو DTCO ، إلى أجهزة مصممة خصيصًا لصنع خلايا وذاكرة قياسية أفضل.

لكن DTCO ليست كافية لمواصلة الحوسبة. تآمرت حدود الفيزياء والواقع الاقتصادي لوضع حواجز في طريق التقدم باستخدام ترانزستور مقاس واحد يناسب الجميع. على سبيل المثال ، حالت الحدود المادية دون انخفاض جهد تشغيل CMOS إلى أقل من 0.7 فولت ، مما أدى إلى إبطاء التقدم في استهلاك الطاقة ، كما توضح أنابيلا فيلوسو ، المهندس الرئيسي في Imec. ساعد الانتقال إلى المعالجات متعددة النواة في حل هذه المشكلة لبعض الوقت. وفي الوقت نفسه ، تعني حدود المدخلات والمخرجات أنه أصبح من الضروري أكثر فأكثر دمج وظائف شرائح متعددة في المعالج. لذا ، بالإضافة إلى النظام على الرقاقة (SoC) الذي يحتوي على مثيلات متعددة من أنوية المعالج ، فإنها تدمج أيضًا الشبكة والذاكرة وغالباً مراكز معالجة الإشارات المتخصصة. لا يقتصر الأمر على أن هذه النوى والوظائف لها طاقة مختلفة واحتياجات أخرى ، بل لا يمكن أيضًا تصغيرها بنفس المعدل. حتى ذاكرة التخزين المؤقت لوحدة المعالجة المركزية ، SRAM ، لا تتقلص بسرعة مثل منطق المعالج.

التحسين المشترك لتكنولوجيا النظام

إن تفكيك الأشياء هو تحول فلسفي بقدر ما هو مجموعة من التقنيات. وفقًا لـ Ryckaert ، تعني STCO النظر إلى نظام على شريحة كمجموعة من الوظائف ، مثل مزود الطاقة ، I / O ، وذاكرة التخزين المؤقت. يقول: “عندما تبدأ في التفكير في الوظائف ، فإنك تدرك أن SoC ليس هذا النظام المتجانس ، بل مجرد ترانزستورات ومترابطة”. “إنها وظائف تم تحسينها لأغراض مختلفة.”

من الناحية المثالية ، يمكنك بناء كل وظيفة باستخدام تقنية المعالجة الأنسب لها. في الممارسة العملية ، هذا يعني في الغالب بناء كل منها على قطعة من السيليكون الخاصة بها ، أو رقاقة. ثم تقوم بربط هؤلاء معًا باستخدام التكنولوجيا ، مثل التكديس ثلاثي الأبعاد المتقدم ، بحيث تعمل جميع الوظائف كما لو كانت على نفس قطعة السيليكون.

أمثلة على هذا التفكير موجودة بالفعل في المعالجات المتقدمة ومسرعات الذكاء الاصطناعي. يتكون مسرع الحوسبة عالي الأداء من Intel Ponte Vecchio (يسمى الآن Intel Data Center GPU Max) من 47 شريحة تم إنشاؤها باستخدام عمليتين مختلفتين ، كل واحدة من Intel و Taiwan Semiconductor Manufacturing Co. AMD تستخدم بالفعل تقنيات مختلفة لشريحة الإدخال / الإخراج وحساب chiplets في وحدات المعالجة المركزية (CPU) الخاصة به ، وبدأ مؤخرًا في فصل ذاكرة التخزين المؤقت عالية المستوى الخاصة بشريحة الحوسبة SRAM.

تذهب خريطة طريق Imec إلى CMOS 2.0 إلى أبعد من ذلك. تتطلب الخطة الاستمرار في تقليص الترانزستورات ، وتحريك الطاقة وربما إشارات الساعة أسفل سيليكون وحدة المعالجة المركزية ، وتكامل أكثر إحكامًا للشرائح ثلاثية الأبعاد. يقول ريكارت: “يمكننا استخدام هذه التقنيات للتعرف على الوظائف المختلفة ، وتفكيك SoC ، وإعادة دمجها لتكون فعالة للغاية”.

سيتغير شكل الترانزستورات خلال العقد القادم ، وكذلك سيتغير المعدن الذي يربط بينهما. في النهاية ، يمكن أن تكون الترانزستورات عبارة عن أجهزة مكدسة مصنوعة من أشباه موصلات ثنائية الأبعاد بدلاً من السيليكون. يمكن وضع توصيل الطاقة والبنية التحتية الأخرى تحت الترانزستورات.إميك

استمرار تحجيم الترانزستور

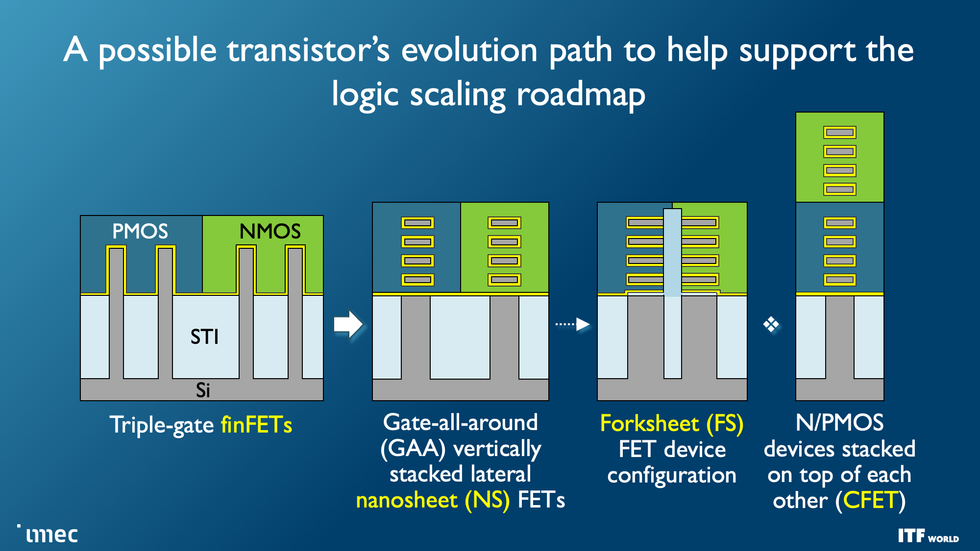

ينتقل صانعو الرقائق الرئيسيون بالفعل من ترانزستورات FinFET التي شغلت العقد الأخير من أجهزة الكمبيوتر والهواتف الذكية إلى بنية جديدة ، ترانزستورات الصفائح النانوية [see “The Nanosheet Transistor Is the Next (and Maybe Last) Step in Moore’s Law”]. في النهاية ، سيتم بناء ترانزستورين من صفائح نانوية فوق بعضهما البعض لتشكيل FET التكميلي ، أو CFET ، والذي يقول Velloso إنه “يمثل أقصى درجات مقياس CMOS” [see “3D-Stacked CMOS Takes Moore’s Law to New Heights”].

نظرًا لتقليص حجم هذه الأجهزة وتغيير شكلها ، فإن أحد الأهداف الرئيسية هو تقليل حجم الخلايا المنطقية القياسية. يتم قياس ذلك عادةً في “ارتفاع المسار” —بشكل أساسي ، عدد خطوط التوصيل البيني المعدنية التي يمكن أن تتلاءم مع الخلية. تعد FinFETs المتقدمة وأجهزة ورقة النانو المبكرة عبارة عن خلايا من ستة مسارات. قد يتطلب الانتقال إلى خمسة مسارات تصميمًا بينيًا يسمى ورقة مفصلية ، والتي تقوم بضغط الأجهزة معًا بشكل أقرب دون الحاجة إلى جعلها أصغر. ستقوم CFETs بعد ذلك بتقليل الخلايا إلى أربعة مسارات أو ربما أقل.

تنتقل الترانزستورات الرائدة بالفعل من بنية الترانزستور ذات التأثير الميداني (FinFET) إلى الصفائح النانوية. الهدف النهائي هو تكديس جهازين فوق بعضهما البعض في تكوين CFET. قد تكون ورقة الشوكة خطوة وسيطة على الطريق.إميك

تنتقل الترانزستورات الرائدة بالفعل من بنية الترانزستور ذات التأثير الميداني (FinFET) إلى الصفائح النانوية. الهدف النهائي هو تكديس جهازين فوق بعضهما البعض في تكوين CFET. قد تكون ورقة الشوكة خطوة وسيطة على الطريق.إميك

وفقًا لـ Imec ، سيتمكن صانعو الرقائق من إنتاج الميزات الدقيقة اللازمة لهذا التقدم باستخدام الجيل التالي من ASML للطباعة الحجرية فوق البنفسجية الشديدة. هذه التقنية ، المسماة EUV ذات الفتحة الرقمية العالية ، قيد الإنشاء في ASML الآن ، وشركة Imec هي التالية في خط التسليم. تؤدي زيادة الفتحة الرقمية ، وهو مصطلح بصري يتعلق بمدى الزوايا التي يمكن للنظام أن يجمع الضوء عليها ، إلى صور أكثر دقة.

شبكات توصيل الطاقة الخلفية

الفكرة الأساسية في شبكات توصيل الطاقة الخلفية هي إزالة جميع الوصلات البينية التي ترسل الطاقة – على عكس إشارات البيانات – من فوق سطح السيليكون ووضعها تحته. يجب أن يسمح ذلك بتقليل فقد الطاقة ، لأن التوصيلات البينية التي توفر الطاقة يمكن أن تكون أكبر وأقل مقاومة. كما أنه يحرر مساحة فوق طبقة الترانزستور للوصلات البينية التي تحمل الإشارة ، مما قد يؤدي إلى تصميمات أكثر إحكاما [see “Next-Gen Chips Will Be Powered From Below”].

في المستقبل ، يمكن نقل المزيد إلى الجزء الخلفي من السيليكون. على سبيل المثال ، ما يسمى بالوصلات البينية العالمية – تلك التي تمتد (نسبيًا) لمسافات كبيرة لنقل الساعة وإشارات أخرى – يمكن أن تذهب أسفل السيليكون. أو يمكن للمهندسين إضافة أجهزة نشطة لتوصيل الطاقة ، مثل صمامات أمان التفريغ الكهروستاتيكي.

تكامل ثلاثي الأبعاد

هناك عدة طرق للقيام بالتكامل ثلاثي الأبعاد ، ولكن الأكثر تقدمًا اليوم هو الترابط الهجين من الرقاقة إلى الرقاقة والموت إلى الرقاقة [see “3 Ways 3D Chip Tech Is Upending Computing”]. يوفر هذان النوعان أعلى كثافة من الترابط بين اثنين من السليكون يموت. لكن هذه الطريقة تتطلب أن يتم تصميم القوالب معًا ، بحيث تتم محاذاة وظائفهما ونقاط الترابط ، مما يسمح لهما بالعمل كرقاقة واحدة ، كما تقول آن جوردان ، العضو الرئيسي في الفريق الفني. Imec R&D في طريقها لتكون قادرة على إنتاج ملايين الاتصالات ثلاثية الأبعاد لكل مليمتر مربع في المستقبل القريب.

الوصول إلى CMOS 2.0

سيأخذ CMOS 2.0 التجزئة والتكامل غير المتجانس إلى أقصى الحدود. اعتمادًا على التقنيات المنطقية لتطبيقات معينة ، يمكن أن ينتج عن ذلك نظام ثلاثي الأبعاد يشتمل على طبقات من الذاكرة المضمنة ، والإدخال / الإخراج والبنية التحتية للطاقة ، ومنطق عالي الكثافة ، ومنطق تيار محرك الأقراص المرتفع ، وكميات هائلة من ذاكرة التخزين المؤقت.

لن يتطلب الوصول إلى هذه النقطة تطوير التكنولوجيا فحسب ، بل يتطلب أيضًا الأدوات والتدريب لتمييز التقنيات التي من شأنها بالفعل تحسين النظام. كما يشير Bardon ، فإن الهواتف الذكية والخوادم ومسرعات التعلم الآلي وأنظمة الواقع المعزز والواقع الافتراضي لها متطلبات وقيود مختلفة تمامًا. ما هو منطقي بالنسبة لأحدهم قد يكون طريقًا مسدودًا للآخر.

من مقالات موقعك

مقالات ذات صلة حول الويب